MITS Altair 8800

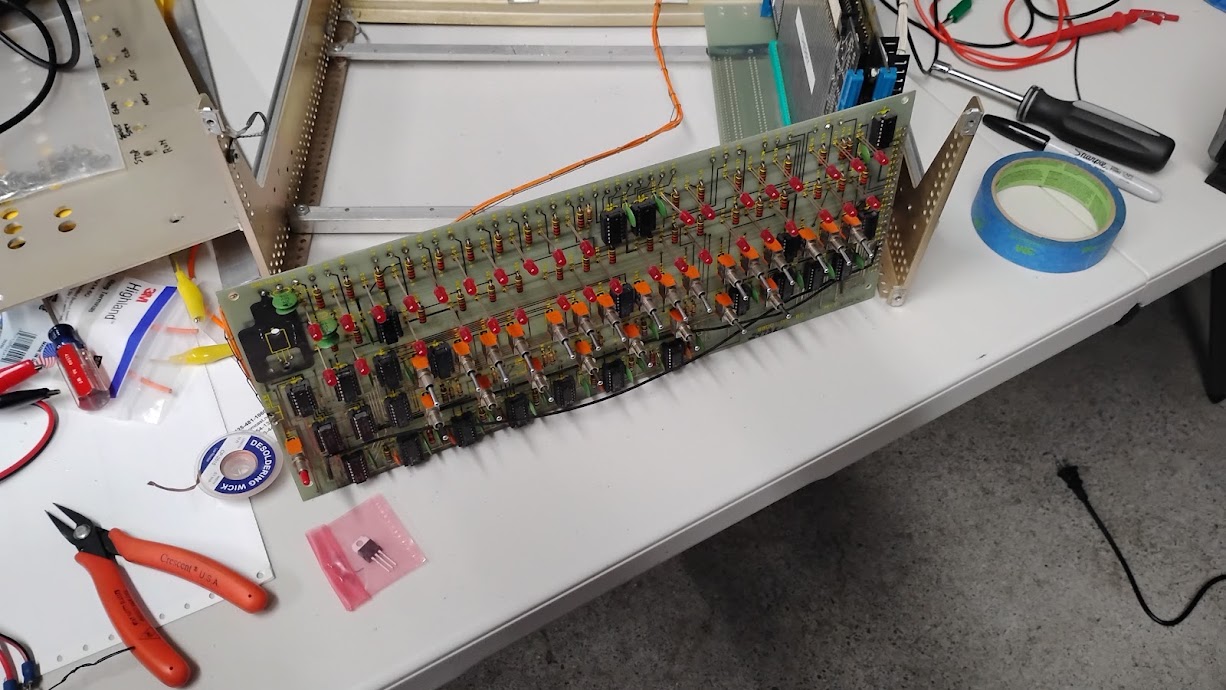

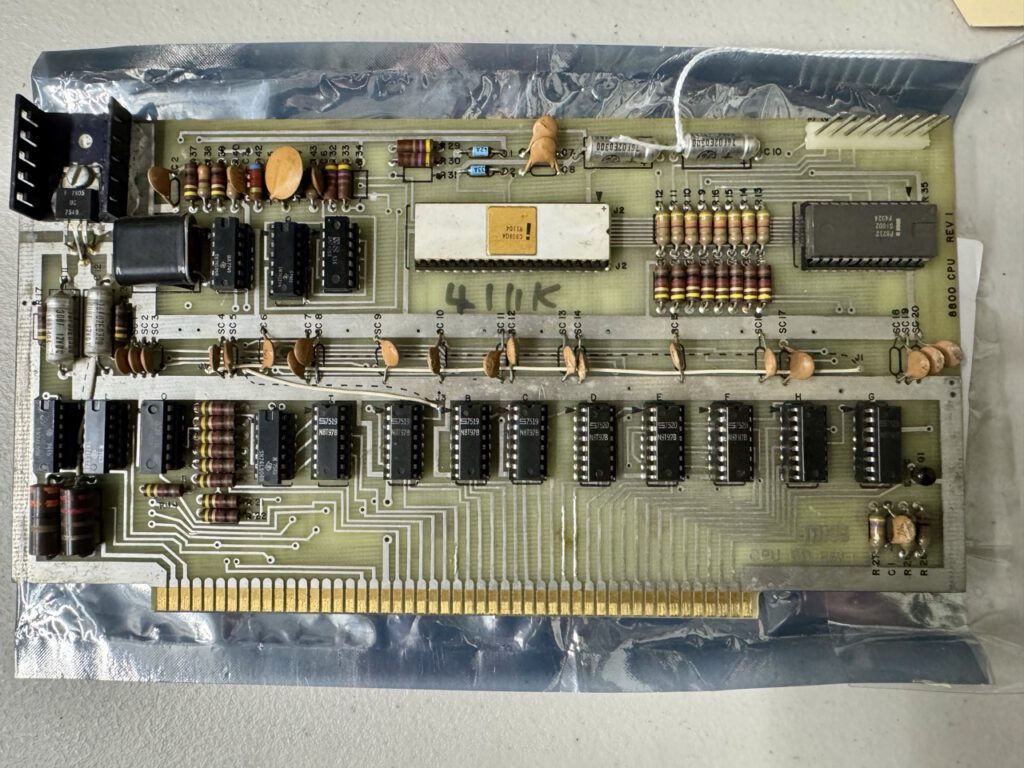

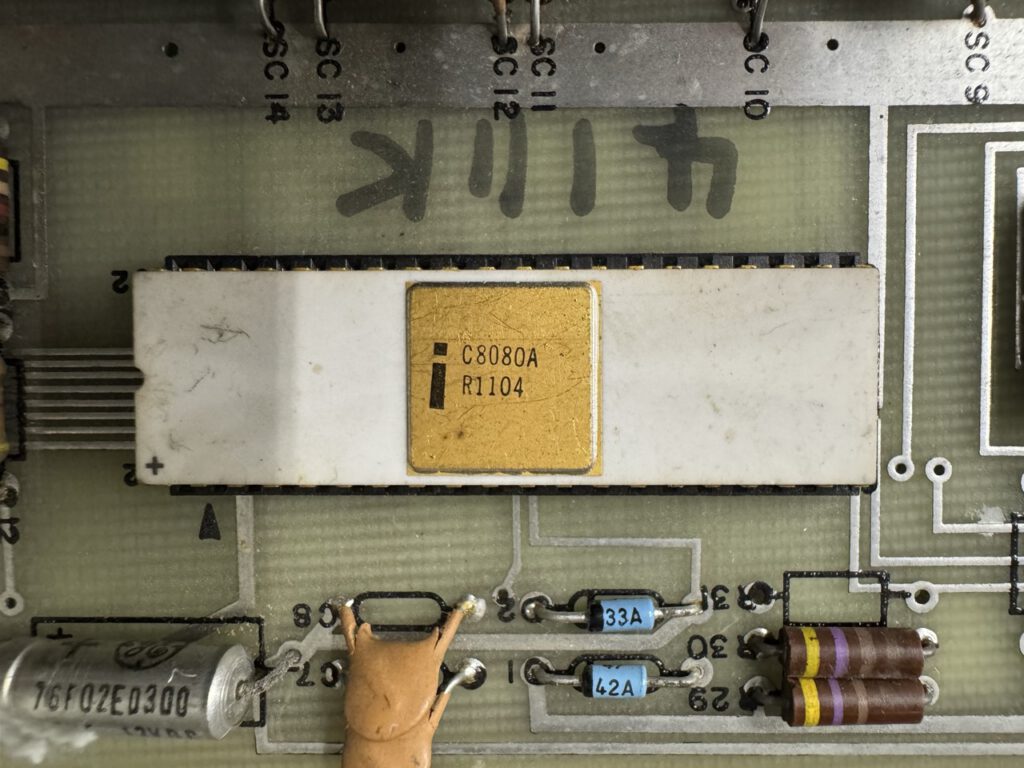

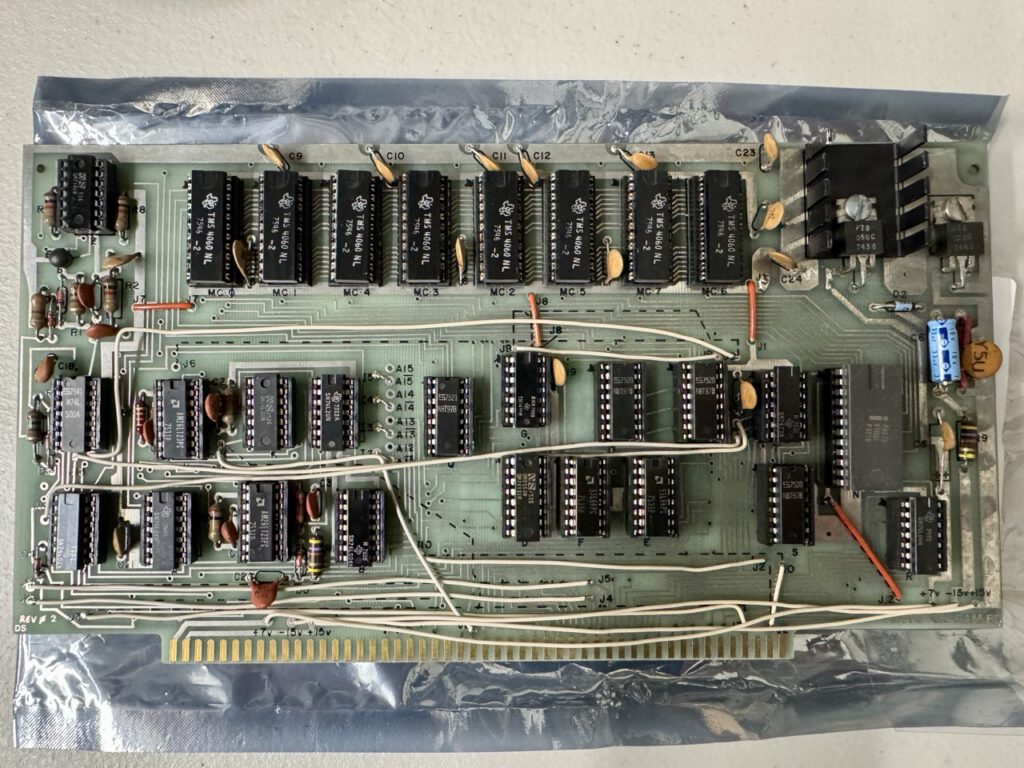

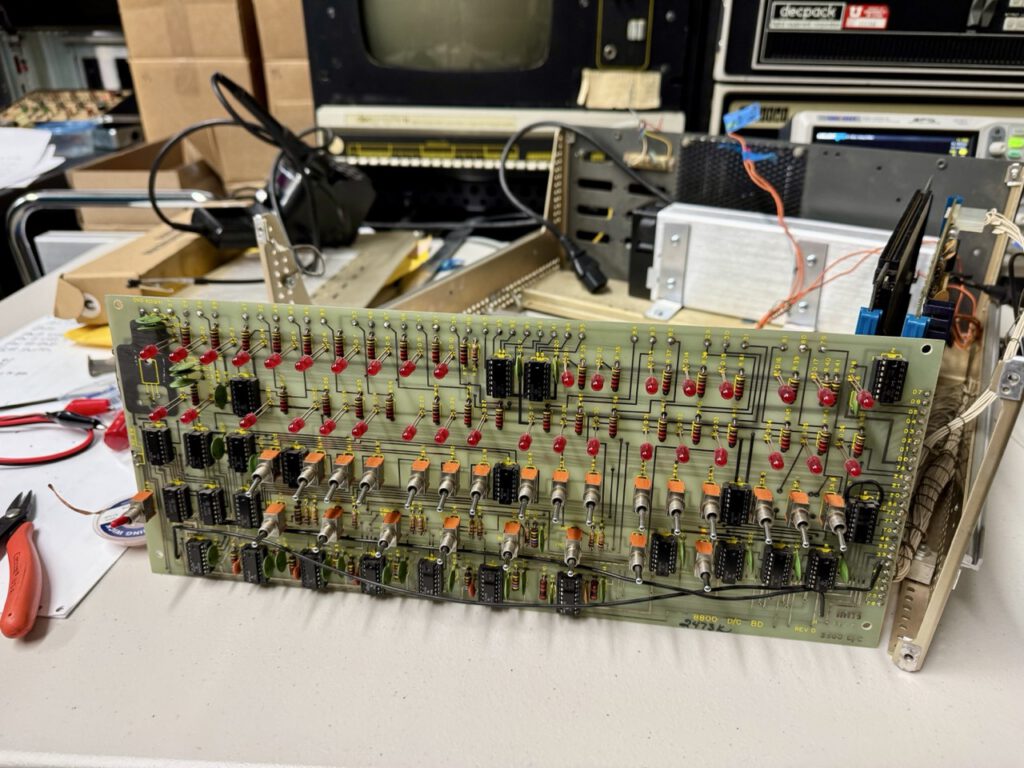

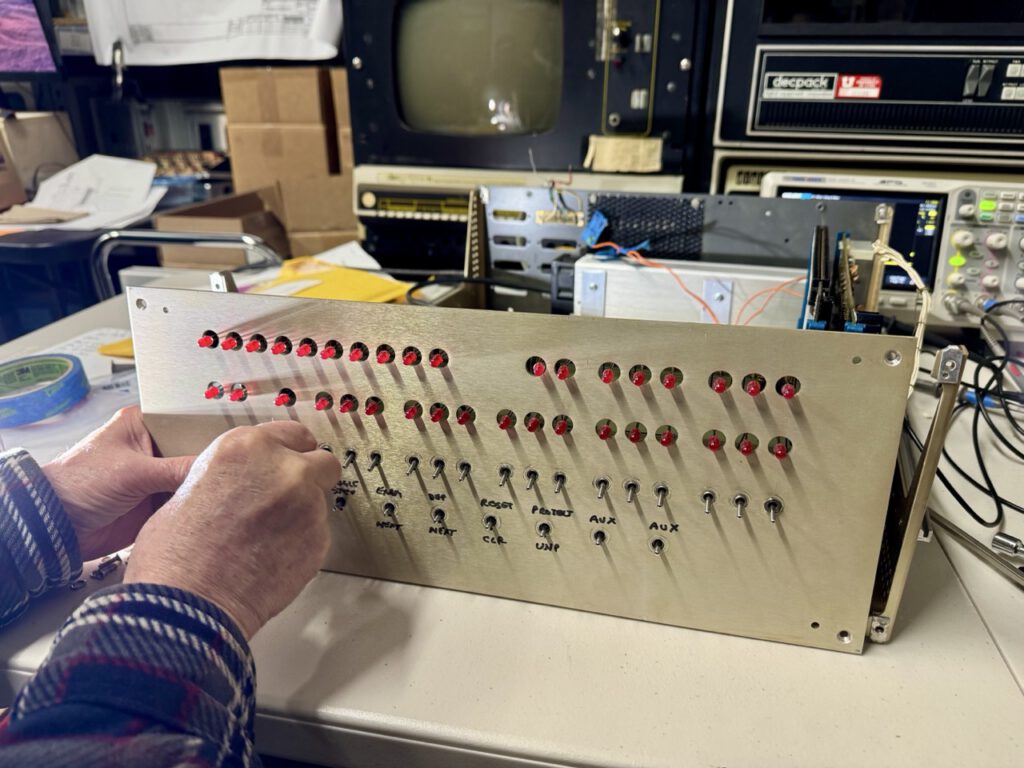

Saturday October 25th, 2025: The power supply has been replaced with a modern unit. The chassis has an CPU board and a 4K static RAM board. Powering on produced some front panel lights, but no switches seemed to be functioning other then reset.

Voltage checks revealed the front panel 5V regulator was putting out about 2V. Regulator replaced and now functions correctly; switches now changing things but not in a coherent way. Run/Stop appears to be controlling the CPU correctly, but Examine and Deposit are dysfunctional.

Sunday October 26th, 2025: Reviewed the Examine logic and developed an understanding of how it should work…

The S100 Address lines on the CPU card are not tri-state; the CPU card is the only device allowed to assert an address; to place an address on the bus, you must coerce the CPU into doing it for you.

The Examine switch sets the CPU to do a single instruction fetch and execute cycle. When the CPU the instruction fetch, the front panel logic places a jump instruction opcode (JMP, 0303) on the data lines. The CPU sees the data lines as the instruction, and executes a JMP; that instructions has a two byte opcode (the jump address). The front panel logic places the low eight bits of the address switches on the data lines, and then the high eight bits. The CPU assembles those bytes into the jump address and puts that address on the bus address lines, and the read operand cycle and halts.

At this point, the contents of the address switches should appear on the address LEDs; they are not.

I scoped the Examine logic, and verified that the sequencer (303, low 8 bits, high bits) logic is correct, but the 303 opcode and the address bytes are not being put on the data lines. That logic is gated be the pDBIN bus signal, which is not being asserted by the CPU, and so the data is never passed to the bus data lines.

So the CPU board is not behaving correctly; the T2 PRDY line from the front panel to the CPU board is being asserted, and that should trigger the pDBIN line to tell the memory (or front panel board) to put the data on the bus.

At this point, we started experiencing apparent thermal issues; the front panel would lockup; turning the system off and letting it cool resolved the issue.

Next steps: locate the overheating component; track signals through the CPU board to see why pDBIN is not being asserted.

Update 10-April-2026

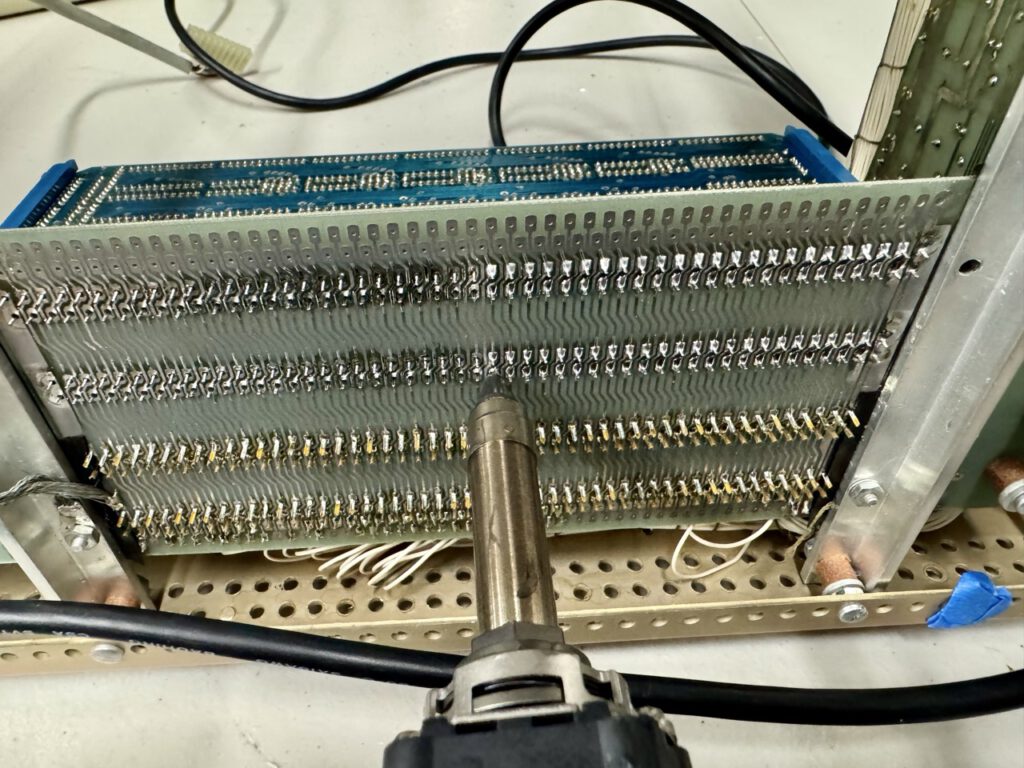

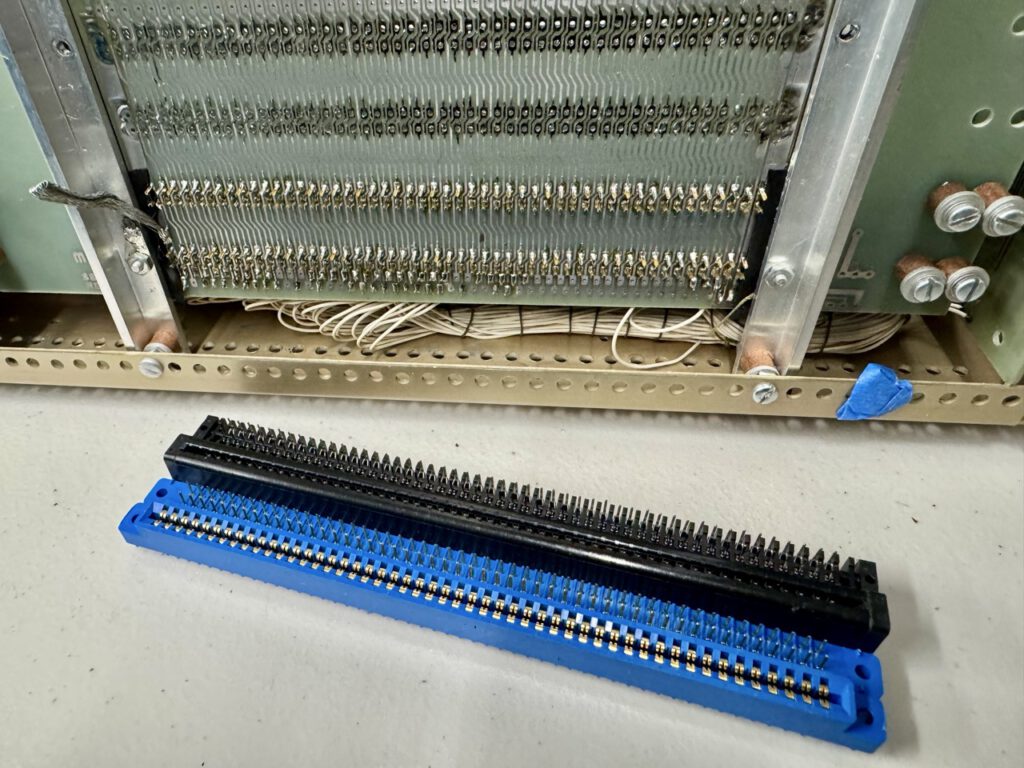

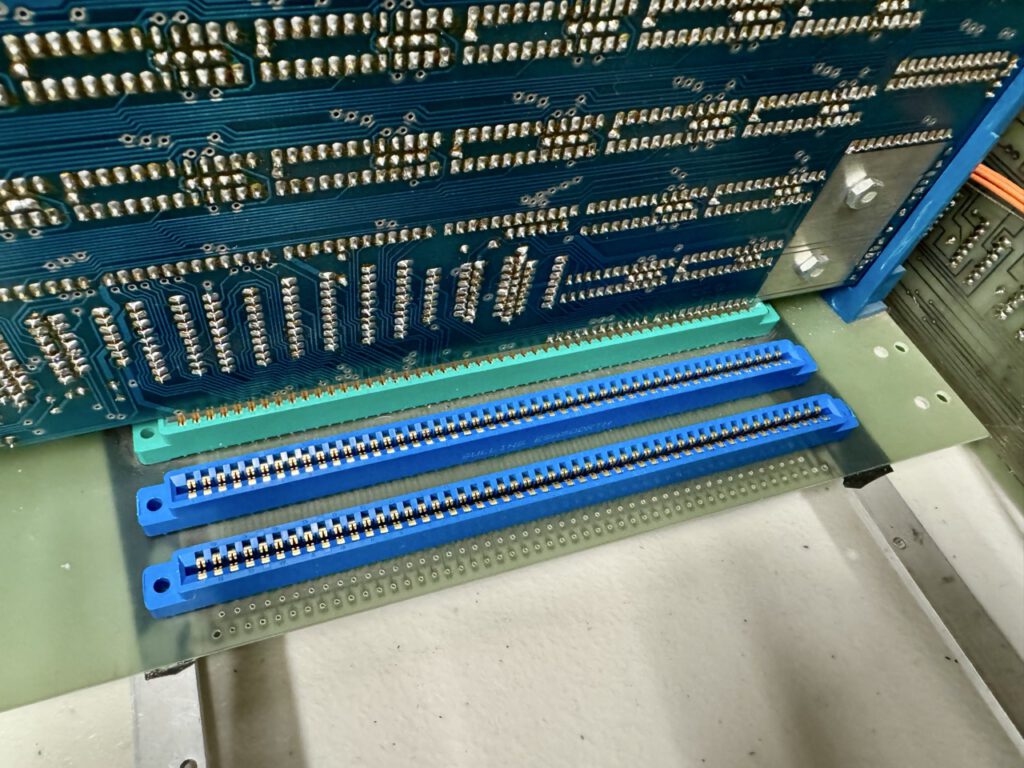

The Altair BUS connectors have a narrower pin pitch than other “100 pin” edge connectors out there. Additionally, a pair of edge connectors we sourced cheaply did not make good contact and would cause the 88-2SIO board to hang. The correct SULLINS connectors were found which fit correctly into the Altair’s backplane. Fortunately desoldering the 200 pins of the incorrect edge connectors was fairly straight forward.